# DESIGN AND ANALYSIS OF 32-BIT REVERSIBLE ALU FOR LOW POWER APPLICATIONS

## Dr D.Srihari

Assoc. Professor Department of ECE, SVCET(Autonomous), Chittoor, AP. Email:sribindu262004@gmail.com.

## S. Nagaraj

Assoc. Professor Dept. of ECE, SVCET(Autonomous), Chittoor, AP. Email:nagarajsubramanyam@gmail.com

## D Himabindu

Asst. Professor, Department of EEE, School of Engg.&Tech.SPMVV,Tirupati, AP. Email: dsri\_hari@rediffmail.com

# Dr S.Senthil

Asso. Professor Department of EEE, SVCET(Autonomous),Chittoor,AP. Email: dhaya\_sen@yahoo.co.in

Abstract—All processors use an Arithmetic Logic Unit (ALU) for operations in logic and mathematics. It is a crucial component of the design of digital systems as well. ALUs, which are found in numerous devices equivalent to computers, smart phones, and calculators, are among the most crucial parts of any system. With logical gates for each one-bit ALU circuit, similar to AND and OR, Verilog HDL was used to develop a 32-bit ALU. Xilinx is used to carry out the design. It uses less power and can operate more quickly than an ALU processor. Reversible logic has been increasingly important in recent years because a critical criterion in low power design, because its capacity to lower power dissipation. More power is used by ALUs created using non-reversible logic gates. Reversible logic has been essential in recent years for low power VLSI Design methodologies as a result of the demand for lower power consumption. This method aids in decreasing power consumption and power loss. This study compares a reversible logic gate-based ALU architecture, such as the Peres gate, Feynman gate, Toffoli gate, and Fredkin gate, as opposed to one that uses ordinary logic gates. ModelSim is used to simulate each module, while Xilinx ISE 14.7 is used to synthesise each module. Index Terms—ALU, Peres gate, Feynman gate, Fredkin gate, Toffoli gate and RI gate

## I. INTRODUCTION

More power is used by ALUs created employing logic gates that cannot be reversed. Reduced power consumption is there- fore necessary. Because it can decreased power consumption, a crucial criteria In the Low Power Design VLSI, reversible logic has become increasingly

important in recent years. ALUs now in use use reversible logic gates, such as AND, OR, and NOT. Although they are simple to construct, they have some significant downsides, including increased complexity, pricey circuits, delayed operation, and inefficient power use. Reversible logic gates are thus used in this architecture. Future technologies like photonic computing, ultra-low power Very Large Scale Integration architecture etc. all make considerable use of reversible logic. Due to the fact that reversible circuits have No information or energy is lost, reversible logic is being researched for use in VLSI circuits with minimal power. Reversible logic design will therefore undoubtedly be im- portant in the future. In this study, a 32-bit reversible arith- metic and logical unit's logical architecture is described and evaluates its efficiency, size, and power in comparison to an irreversible arithmetic and logical unit.

### II. REVERSIBLE LOGIC GATES

The  $n \times n$  logic circuits that make up reversible logic gates in which there is always a 1:1 mapping between the quantity of inputs and outputs. This makes sure that the only way to redeem input is through the outputs. Quantum costs, garbage outputs, constant inputs, and gate count are the factors that determine how well a reversible circuit performs.

Fig. 1. Reversible Logic Gate

The following is a quick description of the reversible gates utilised in 32-Bit ALU architectures.

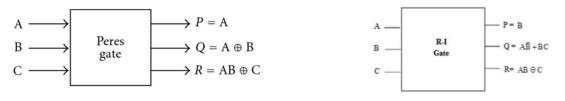

#### A. Peres Gate

Figure 1 shows it a 3 x 3 reversible gate. Here, we employed the Peres gate to achieve the ALU's low quantum cost of 4. Below figure 1 Shows, the inputs and outputs.

Fig. 2. Peres Gate

#### **B.** Feynman Gate

Quantum cost of 1 is associated with the Feynman gate is sometimes referred to a NOT logic gate. The following figure 2 lists the inputs and outputs.

#### Fig. 6. RI Gate

#### III. 32-BIT REVERSIBLE ALU

Fig. 3. Feynman Gate

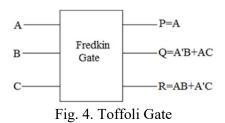

### C. Toffoli Gate

A 3 x 3 gate that can be reversed. The below figure 3 lists the inputs and outputs. The alternate term pertaining to this gate, that has a 5 quantum cost, is the "Doubly controlled NOT gate."

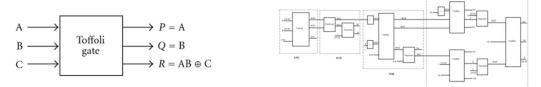

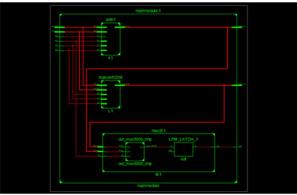

The block diagram a 32-Bit ALU Reversible is displayed in the image below. The ALU must primarily perform the operations AND, XOR, NOR, and SUM. Every action requires a unique circuit design, which is coupled to achieve the lowest possible lines and gate costs. A 4:1 reversible multiplexer is utilised to obtain the output in a single line. The multiplexer employs Fredkin gates. The ALU is termed AXONS ALU by using a letter from each of the operations it performs, which are AND, XOR, NOR, and SUM. It features two selection lines.

#### D. Fredkin Gate

# Fig. 7. 32-BIT REVERSIBLE ALU BLOCK DAIGRAM

It is a reversible 3 x 3 gate. Below Figure 4 shows the inputs and outputs. Quantum cost is 5.

#### **IV. METHODOLOGY**

#### E. RI Gate

Fig. 5. Fredkin Gate

Using Verilog HDL, a 32-bit ALU with Normal and Re- versible logic gates will be developed. At the conclusion, speed, power, and area (the number of LUTs) parameters of ALUs created using both conventional and reversible logic gates are compared. An ALU with reversible gates—such as Peres, Feynman, and other gates—will be used, which reduces power

consumption and delay and boosts circuit performance.

One XOR, one OR, one NOT, and three AND gates are required for this 3 x 3 reversible gate. Modelsim is used to simulate the design, and Xilinx is used to synthesise it.

# V. SIMULATION SYNTHESIS AND POWER RESULTS

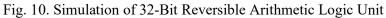

Fig. 11. Synthesis of 32-Bit Normal Arithmetic Logic Unit

Fig. 12. Synthesis of 32-Bit Reversible Arithmetic Logic Unit

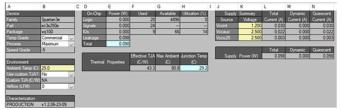

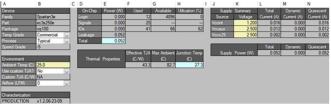

Fig. 13. Power Report of 32-Bit Normal Arithmetic Logic Unit

Fig. 14. Power Report 32-Bit Reversible Arithmetic Logic Unit

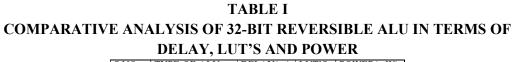

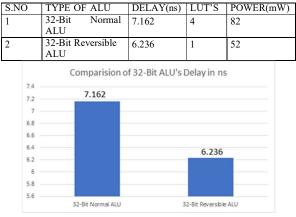

Fig. 15. COMAPARISION OF 32-BIT ALU'S DELAY

| 185 | $\supset$ |

|-----|-----------|

|     |           |

#### Semiconductor Optoelectronics, Vol. 42 No. 02 (2023) https://bdtgd.cn/

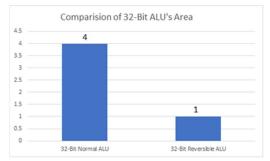

Fig. 16. COMAPARISION OF 32-BIT ALU'S AREA

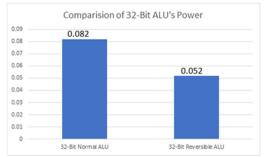

Fig. 17. COMAPARISION OF 32-BIT ALU'S POWER

# VI. CONCLUSION

In this research, we used logic gates and reversible logic gates to develop and analyse a variety of ALUs, including 16-bit and 32-bit versions. Reversible gates are utilised in the creation of reversible 16-bit and 32-bit ALUs in place of regular gates. Reversibility reduces power consumption as well as pieces of data are used and lost. Logical reversibility has been the topic of discussion. By employing reversible logic gates, the area, power, and delay of a 32-Bit ALU are all decreased by 25%, 63%, and 87%, respectively. The project's future scope involves using the optimised ALUs.

## REFERENCES

"Arithmetic & Logic Unit (ALU) Design Using Reversible Control Unit," ISSN: 2277-3754 IIJEIT, Volume 1, Issue 6, June 2012, ISO 9001:2008 Certified.

[2] "IJARCCE, Vol. 2, Issue 10, Oct 2013, "Design & Synthesis of 16-bit ALU utilising Reversible Logic Gates"

[3] "A Review of Reversible Gates and its Application in Logic Design," AJER, Volume-03, Issue-04, Jul 2014, pp. 151–161.

[4] "Design & Implementation 16-Bit Reversible Logic ALU with 15 Operations", IJAREEIE, Volume 3, Issue 4, Apr 2014

[5] "Implementation of 16 bit ALU utilising Toffoli Reversible gates,"

IJISET, Vol. 1 Issue 6, Aug 2014. ISSN 2348 - 7968

[6] "16 Bit ALU Based on Very Large-Scale Integration with Interfacing Circuit" IJIERE, Volume 2, Issue 3, 2015

[7] "Design of Low Power Arithmetic & Logic Unit Using Reversible Logic Gates",International Journal of Very Large-Scale Integration System Design and Communication Systems, ISSN 2322-0929, Vol. 3, Issue. 3, Jun 2015, Pages: 0271–0276

[8] "Design of Reversible Arithmetic & Logic Unit (ALU) Using VH- SIC (Very High Speed Integrated Circuit) Hardware Description Lan- guage",IJMETMR, Volume No: 2 (2015), Issue No: 8. ISSS No. 2448—4845. (aug)

[9] "A 16-bit ALU's ideal Very Large-Scale Integration design", ICTRC 2015

[10] IRJET, e-ISSN: 2395 -0056 Volume: 03 Issue: 05, May-2016,p-ISSN: 2395-0072, "Design and Implementation of 32-bit ALU with 16 opera- tions using 1-Bit ALU and Reversible Logic Gates"

[11] IJTSR International Open Access Journal, Apr-2017 ISSN No: 2456- 6470 Volume — -2,ISSUE — 1 " Simulation of 16 bit ALU using Verilog-hdl "

[12] "A Novel Design of Reversible Logic based 1-Bit and 4-Bit ALU," IJSER, Volume 8, Issue 3, Mar-2017 ISSN 2229-5518.

[13] "Design & Implementation of Reversible Logic ALU With Four Op- erations", May-2017, IOSR-JECE, e-ISSN: 2278-2834, p-ISSN: 2278- 8735, PP. 55-59

[14] Reversible Logic Gates & Its Performances, Proceedings of the Second IICISC 2018, IEEE Xplore Compliant, ISBN: 978-1-5386-0807-4, May 2018.

[15] "Design & Implementation Of 8 Bit and 16 Bit ALU Using Verilog Language", 2018, Vol. 3, Issue 2, ISSN No. 2455-2143, Pages 30-34 Online since Jun 2018 at IJEAST

[16] IJERA ISSN: 2248-9622, Vol. 10, Issue 8, (Series-V), Aug 2020, pp. 33–38, "Optimized Reversible ALU", Apra meya R S, et al.

[17] Greeshma Arya et al., "Performance Analysis of ALU with Reversible Logic",Jul-Aug2020 IJACSE

[18] "Reversible Logic Gates Design & Implementation of ALU and PAL", Journal of Engineering Science, Vol. 11, Issue 11, Nov. 2020, ISSN 0377-9254.

[19] "Review on Design and Analysis of ALU Using Reversible Logic Gates", Volume 3, Issue 2, Feb 2022 SSN (Online): 2582-7839, IJRAMR

[20] "A System based on AI and ML enhanced to investigate physiological markers for user forecasting decision-making", Semiconductor Optoelectronics, Vol. 44, Issue 1, 2023, ISSN 1001-5868.